IEEE EMC Society Distinguished Lecturer Seminar: Signal Integrity of TSV-Based 3D IC

> July 21, 2010 Joungho Kim at KAIST

joungho@ee.kaist.ac.kr http://tera.kaist.ac.kr

1

# Contents

- 1) Driving Forces of 3D Package and IC

- 2) Signal Integrity Design

- 3) Noise Coupling Issues

- 4) Noise Isolations

- 5) Summary

# 3D Movie

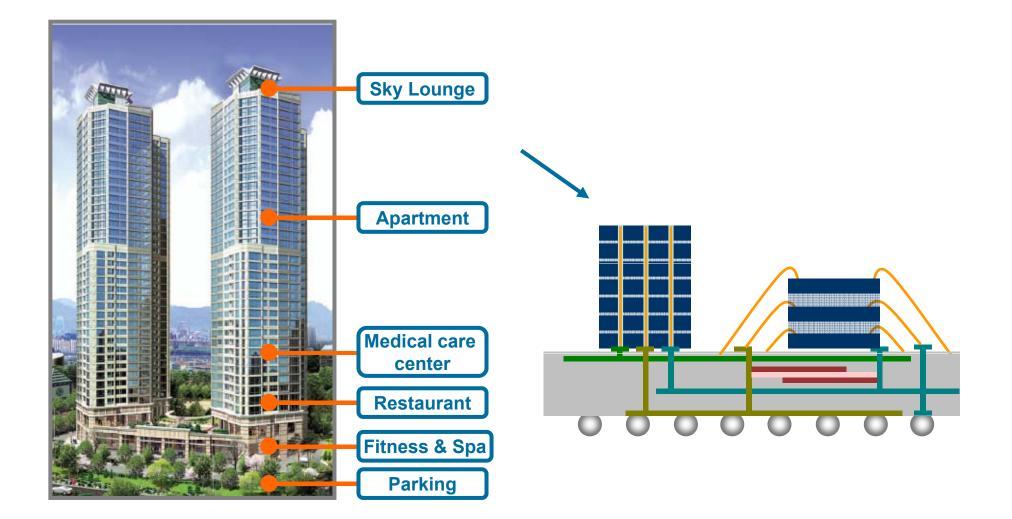

# 3D Housings

KAIST

TERA Terahetz Infeconnection and Package Laboratory

Terahertz Interconnection and Package Laboratory

4

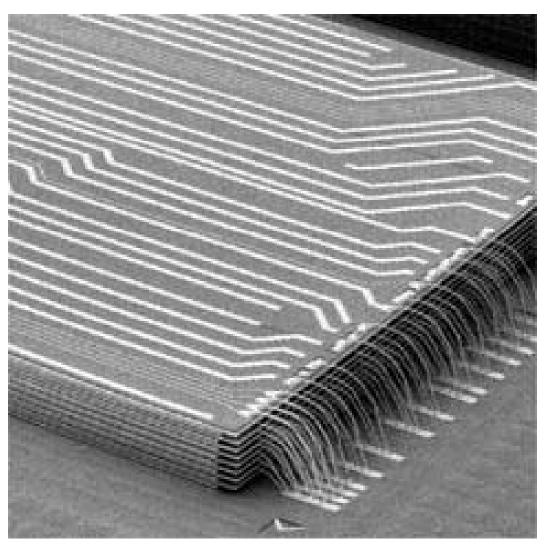

# 16GB Samsung NAND Flash, 8Gbx16

Terahertz Interconnection and Strapp; Moriting Kataa

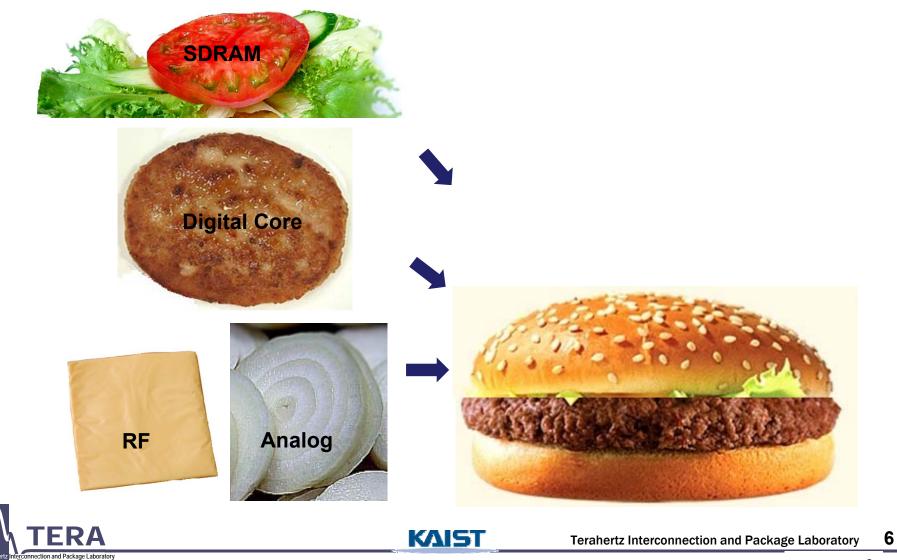

# 3D Hamburger

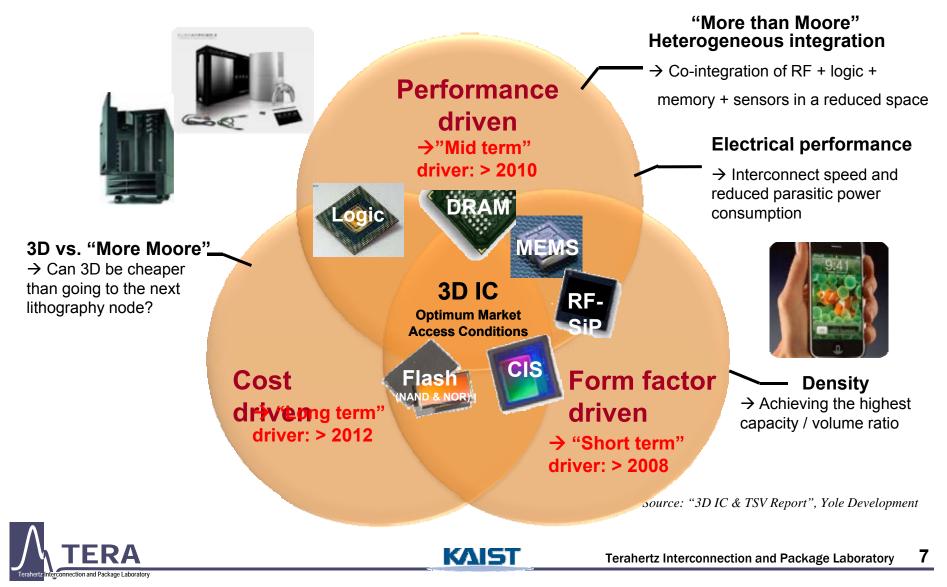

# Expected Market of 3D IC

### Market Driving Forces of 3D IC

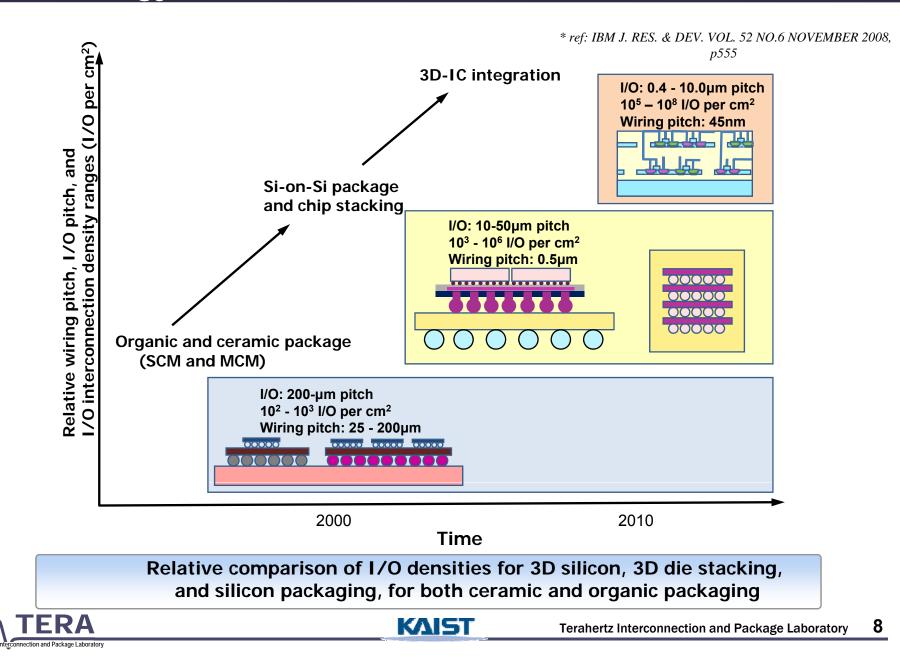

# Technology Trend of 3D IC

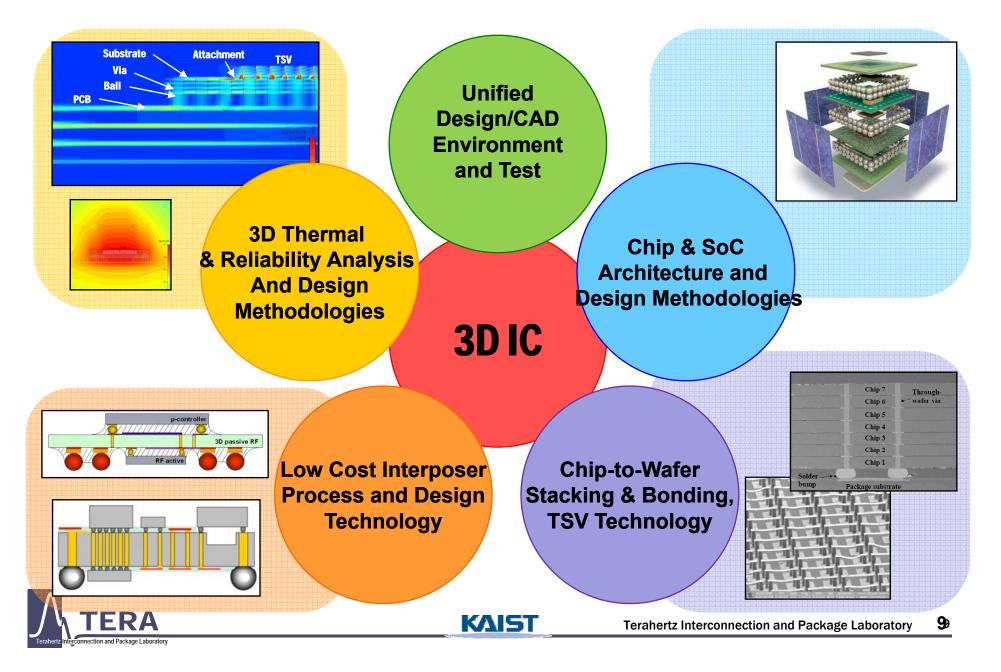

# Core Technologies of 3D IC

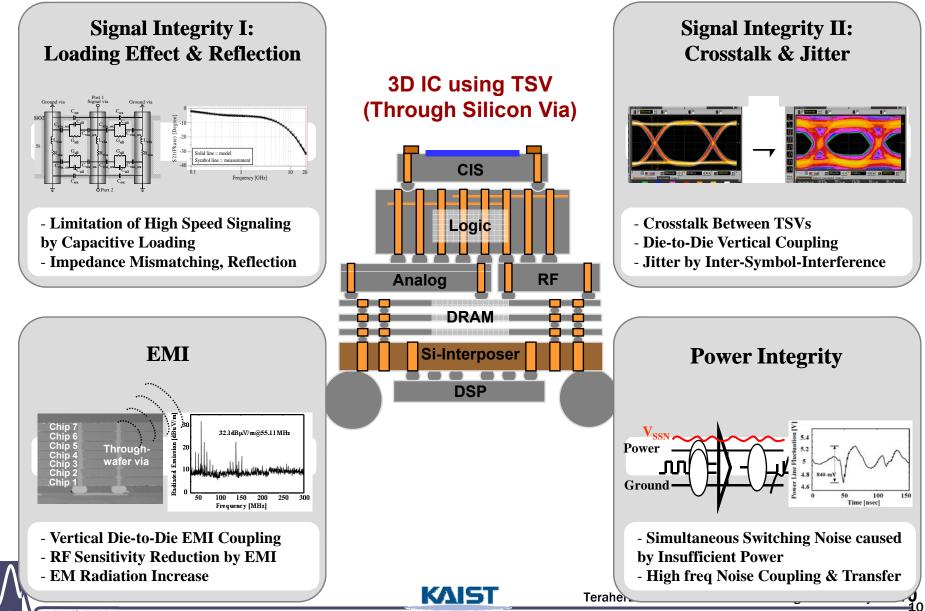

# Signal Integrity Design Issues in 3D IC

erconnection and Package Laboratory

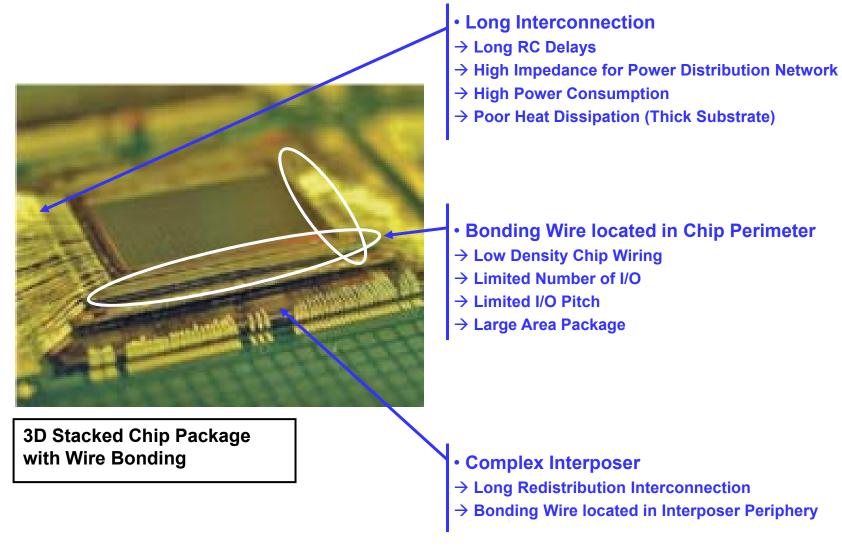

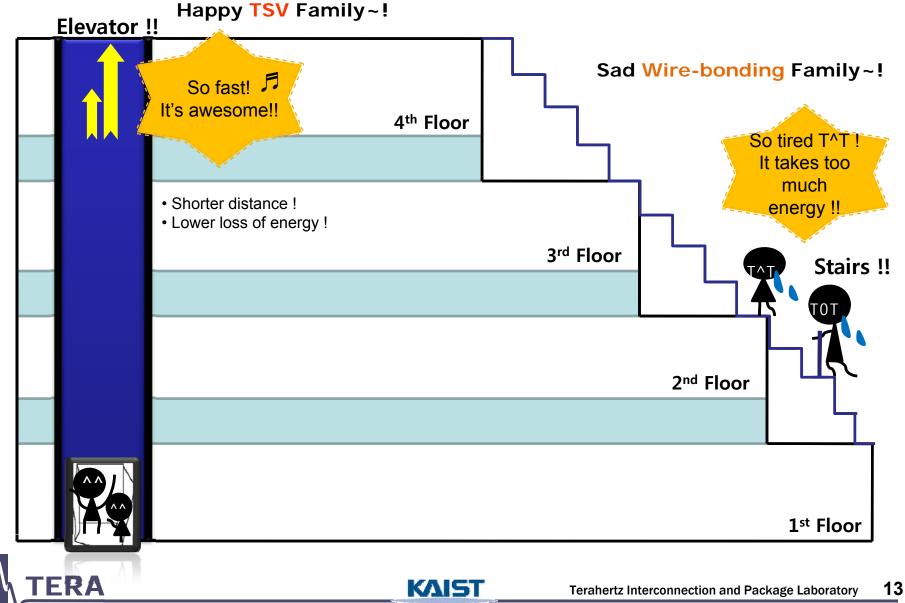

### **Disadvantages of Wire Bonding Stacked Chip Package**

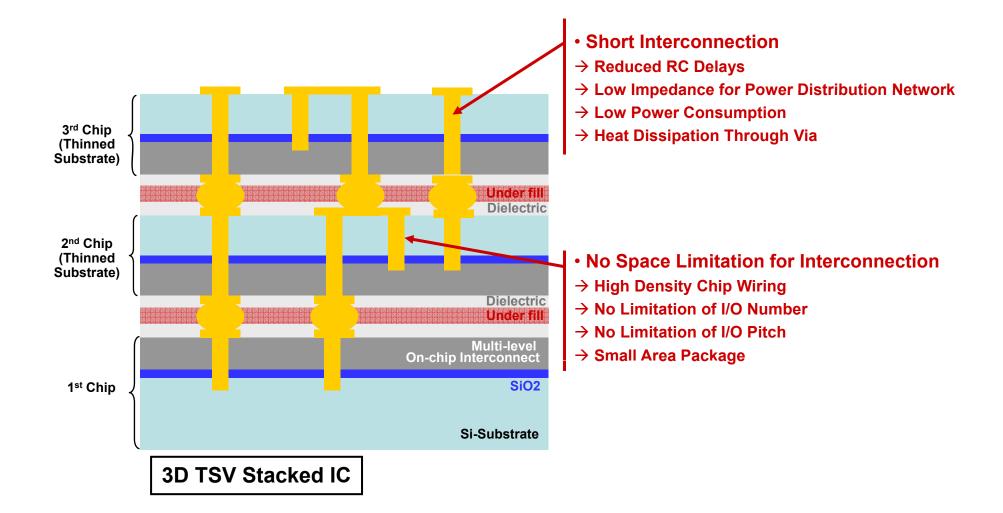

#### Key Technology : TSV (Through Silicon Via)

KAIST

Terahertz Interconnection and Package Laboratory 12

# ★ Why does TSV Family happy ^ ^ ?

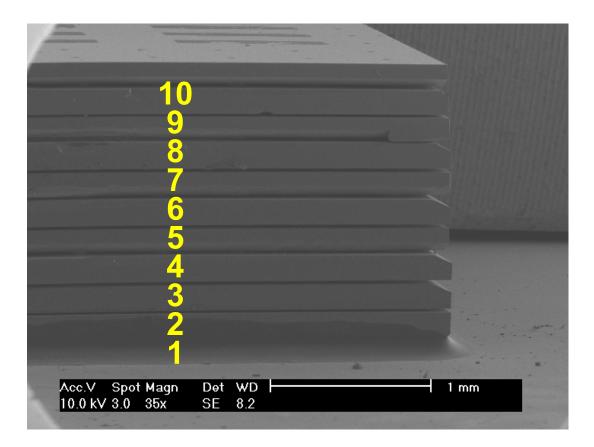

# **10 chip stacked Package by KAIST**

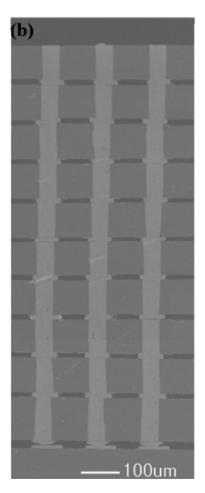

55 μm TSV diameter 150 μm Pitch

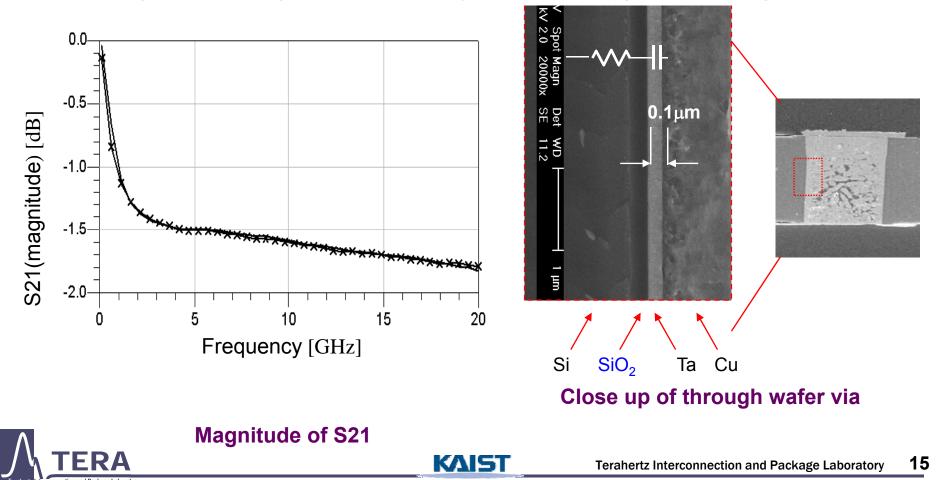

# Background(1): High-frequency Channel Loss in TSV

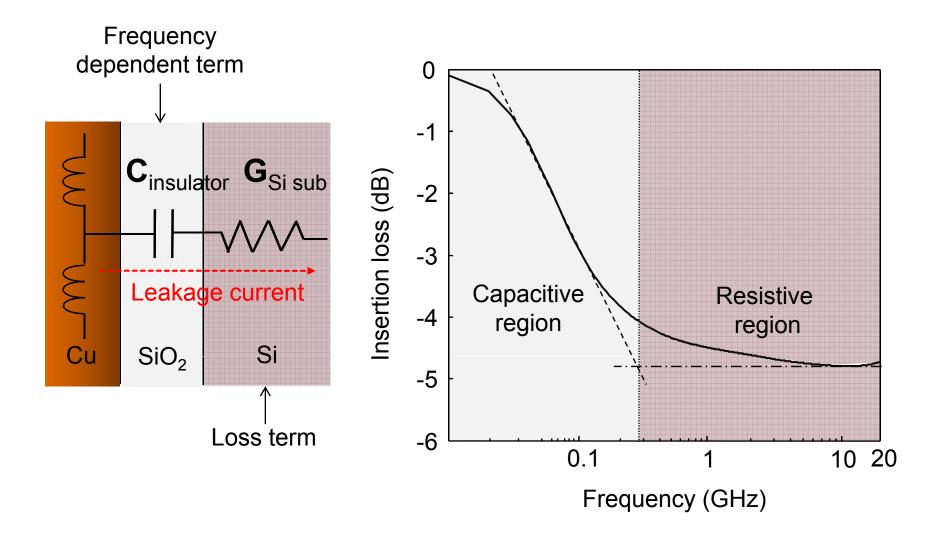

-Significant high-frequency signal loss occur at Signal Transmission Through TSV -The signal loss through TSV is caused by substrate leakage and coupling

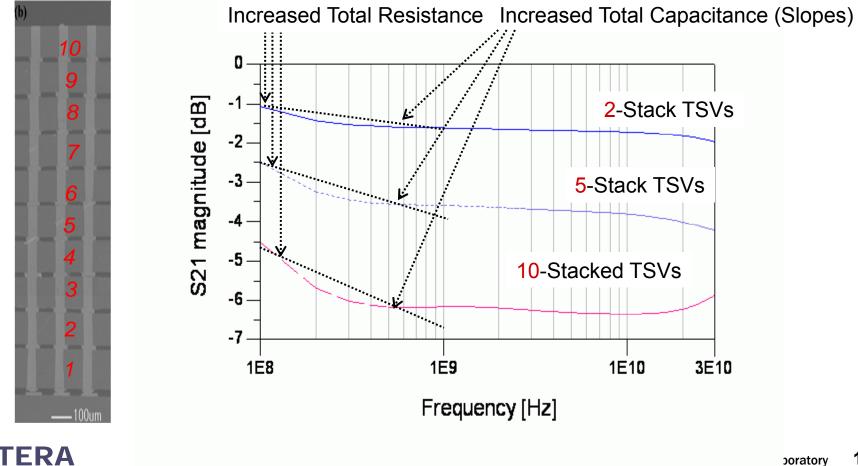

### Background(2): Increased Channel Loss in Multi-Stack TSV

- -Signal loss increases substantially with number of stacks/TSVs

- -The signal loss through TSV is caused by substrate leakage and coupling

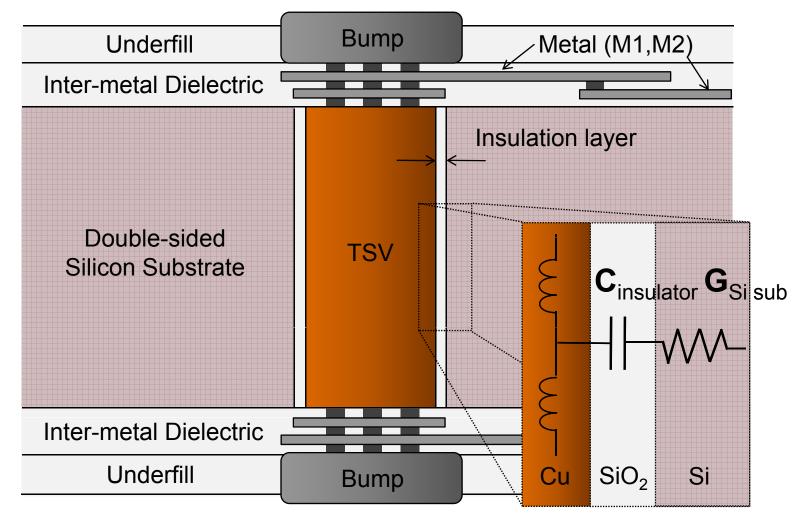

# A Through Silicon Via Structure on Double-sided Silicon

# Frequency-dependent Loss of Through Silicon Via

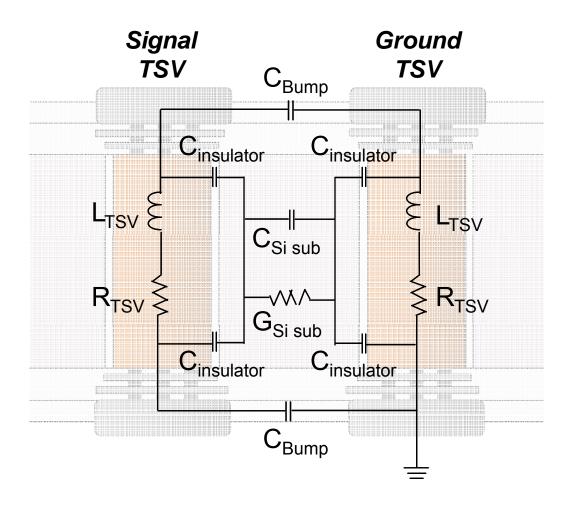

# Scalable Equivalent Circuit Model of a TSV

KAIST

#### **Structural Parameters**

| TSV diameter     | : d |

|------------------|-----|

| TSV-to-TSV pitch | :р  |

| SiO2 thickness   | : t |

| Height           | : h |

| Bump diameter    | : D |

#### **Equations**

$\begin{array}{l} C_{\text{insulator}}\left(d,h,t\right)\\ C_{\text{Si sub}}\left(d,h,p,t\right)\\ C_{\text{Bump}}\left(p,D\right)\\ G_{\text{Si sub}}\left(d,h,p,D\right)\\ R_{\text{TSV}}\left(d,h\right)\\ L_{\text{TSV}}\left(d,h,p\right) \end{array}$

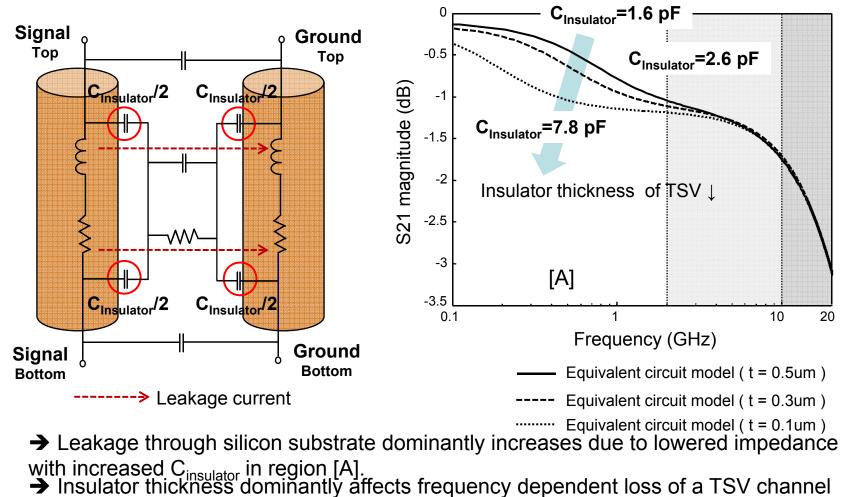

### Analysis of a TSV Channel with Insulator Thickness of TSV

Insulator thickness of TSV (t)

KAIST

Terahertz Interconnection and Package Laboratory 2020

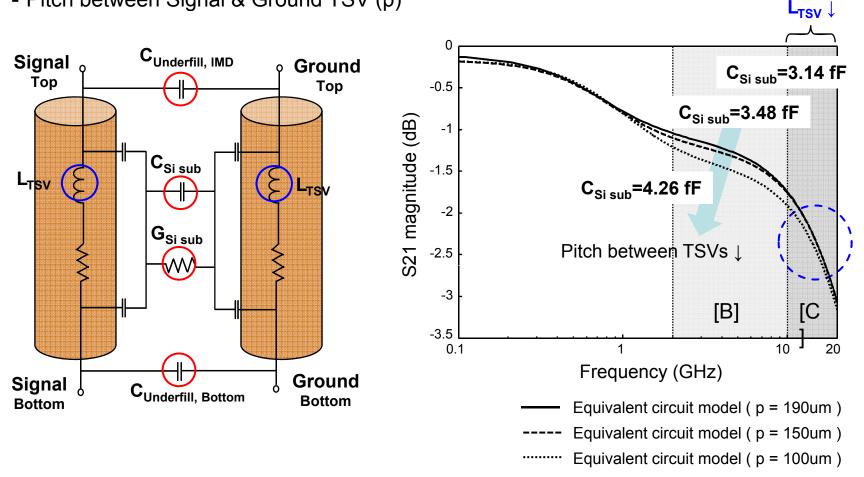

### Analysis of a TSV Channel with Pitch between TSVs

Pitch between Signal & Ground TSV (p)

→ Due to relative small capacitance, pitch affects frequency dependent loss of a TSV channel from region [B].

→ From region [C], inductance effect becomes dominant.

Pitch dominantly affects frequency dependent loss of a TSV channel in region [B].

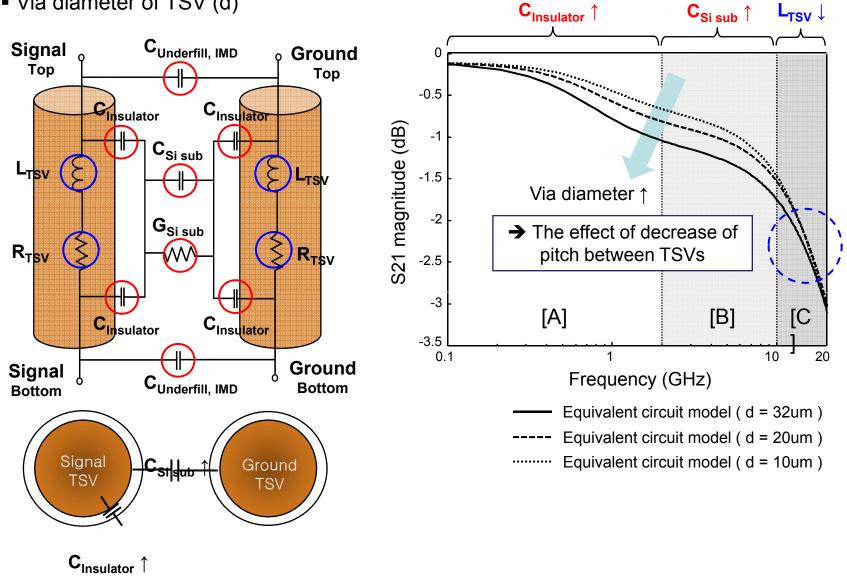

#### Analysis of a TSV Channel with TSV Diameter

Via diameter of TSV (d)

→ Via diameter affects frequency dependent loss of a TSV channel, dominantly Terahertz Interconnection and Package Labora egion [A] and [B] Terahertz Interconnection and Package Laboratory 222

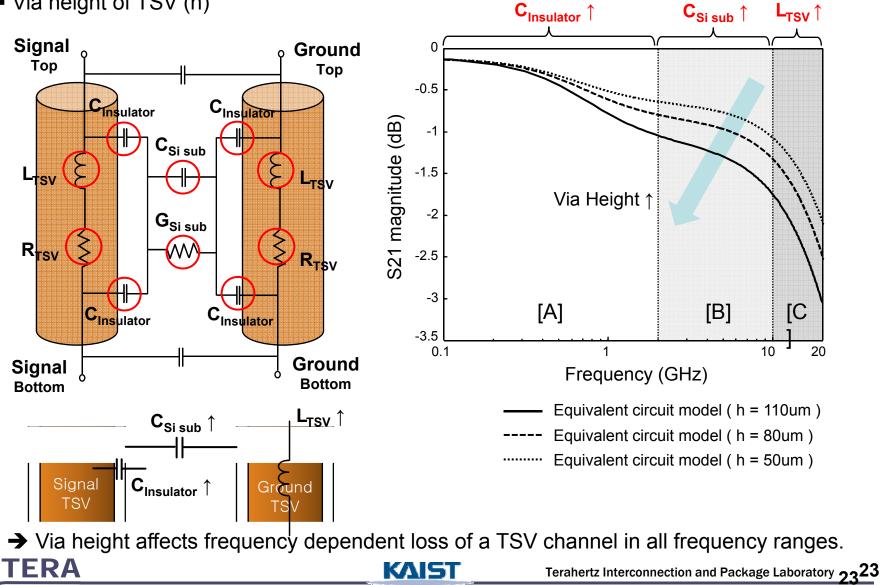

### Analysis of a TSV Channel with Via Height of TSV

Via height of TSV (h)

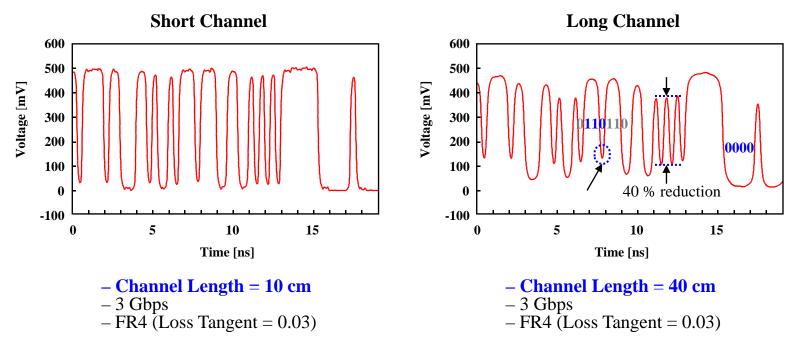

# Inter-symbol Interference (ISI) by Channel Loss

# Inter-symbol Interference is the interference between adjacent pulses of a data

- The channel BW Limit degrades the signal quality

- It depends on line-length, data rate and sub. materials on PCB

[ ISI effect due to line-length ]

KAIST

Terahertz Interconnection and Package Labgratory 24

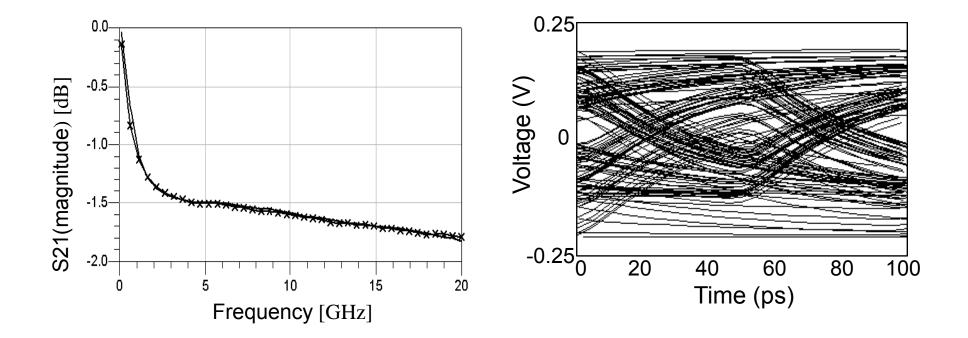

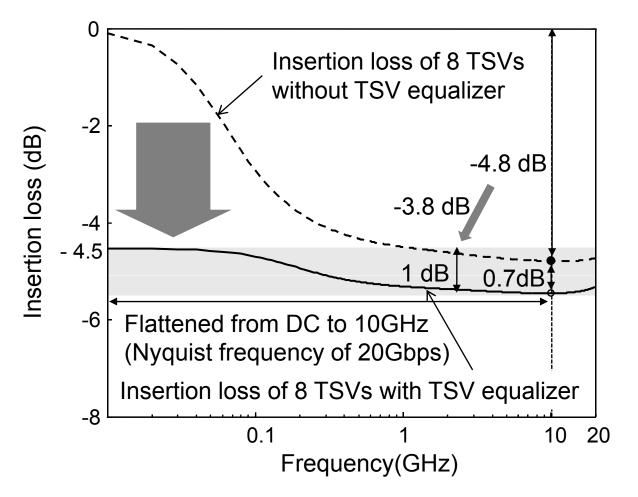

### Inter-Symbol Interference at the TSV Equalizer

#### Magnitude of S21

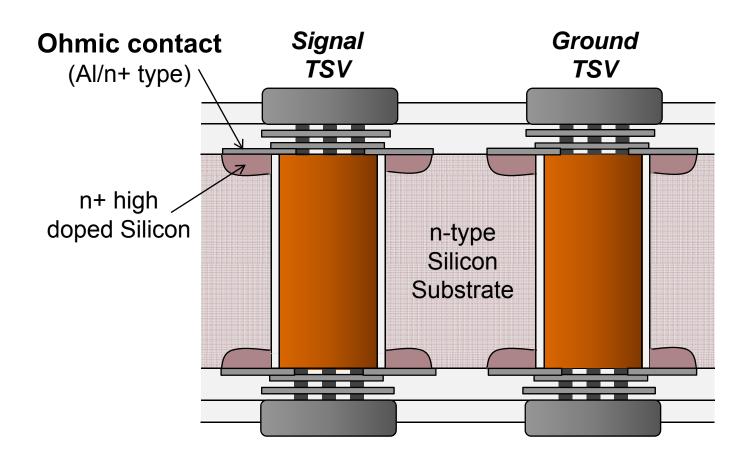

# The Proposed TSV Equalizer using an Ohmic Contact

We intentionally made leakage by using an Ohmic contact resulting in DC attenuation between signal and ground TSV.

# Frequency Domain Simulation-based Verification of the TSV

Equalizor Dorformanco

We successfully flattened frequency dependent loss by 3.8 dB by using TSV Equalizer.

KAIST

Terahertz Interconnection and Package Laboratory

2**27**

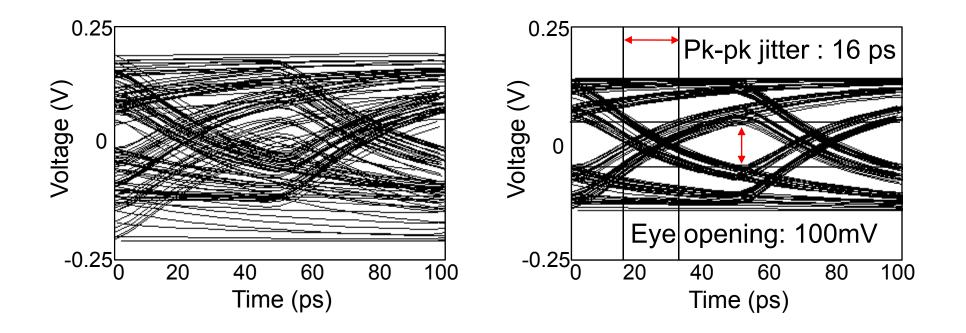

# Time Domain Simulation-based Verification of the TSV

#### Equalizor Porformanco

• We successfully achieved normalized pk-pk jitter and eye-opening, 32% and 20%,

meanwhile the unequalized eye is completely closed.

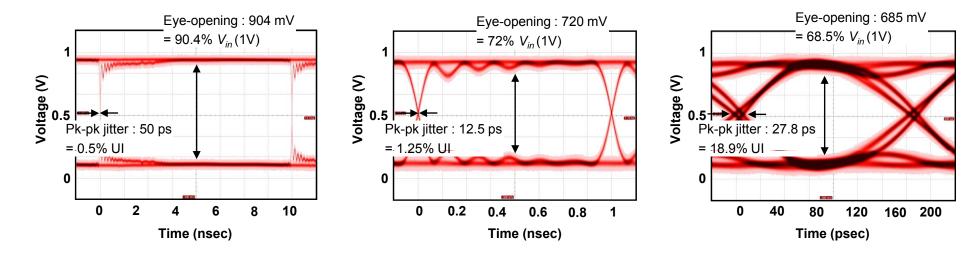

### Time-Domain Measurement Results

#### Measured Eye-diagrams of a TSV channel

- Data rate : 100 Mb/s

- Data Pattern : PRBS 2<sup>11</sup>-1,

- Source amplitude : 1 V

- Data rate : 1 Gb/s

- Data Pattern : PRBS 2<sup>11</sup>-1,

- Source amplitude : 1 V

- Data rate : 5 Gb/s

- Data Pattern : PRBS 2<sup>11</sup>-1,

- Source amplitude : 1 V

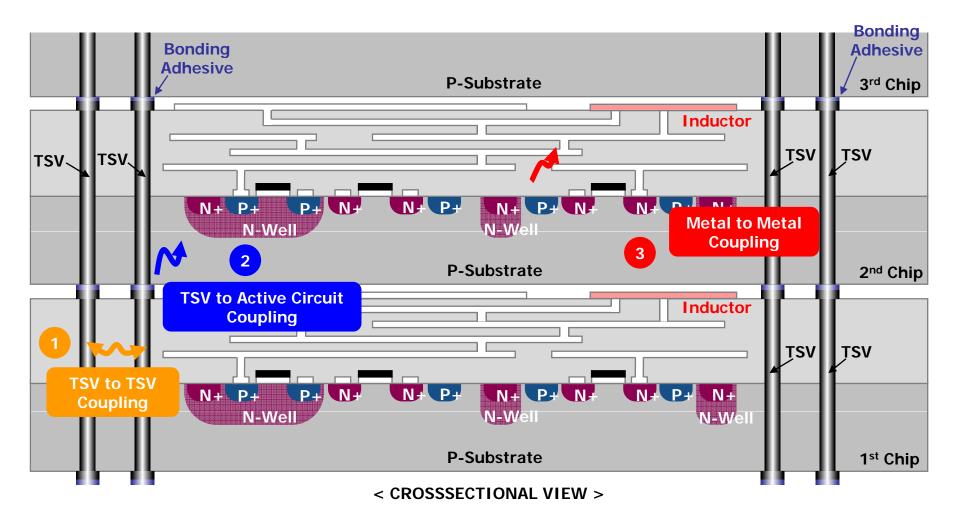

### Coupling Issues in Stacked Dies using TSV

KAIST

Terahertz Interconnection and Package Laboratory **30**

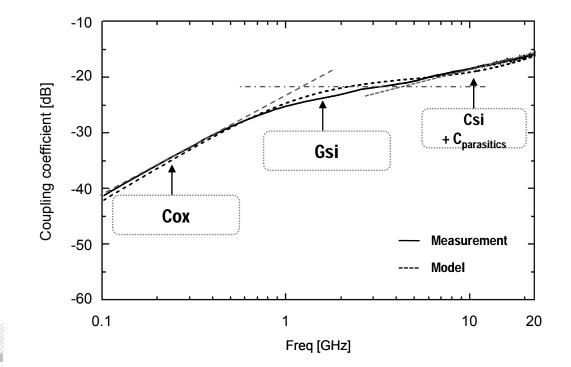

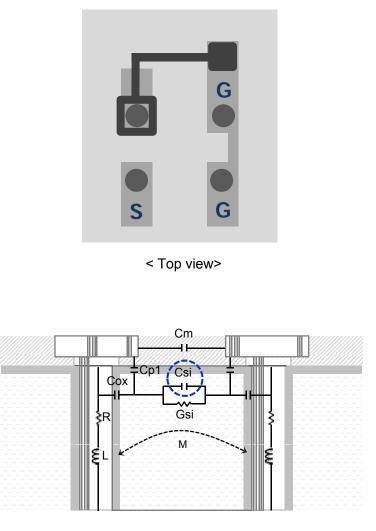

## **Measurement Result of Coupling between TSVs**

S G S G

< Top view>

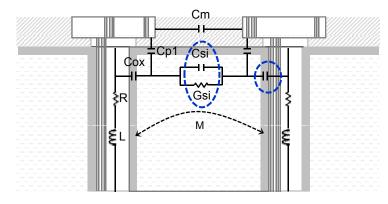

• Analytic model of coupling between TSVs shows good agreement with measurement result

< Equivalent circuit model of coupled TSV>

Terahertz Interconnection and Package Laboratory 31

# Shielding Methods for TSV Coupling

- 1) Re-design of TSV materials and dimensions

- 2) Separation

- 3) Guard Ring

- 4) GND Shield TSV

- 5) Metal Ring

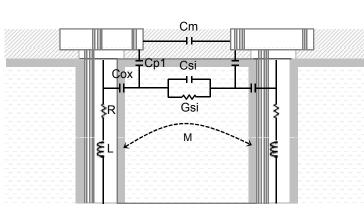

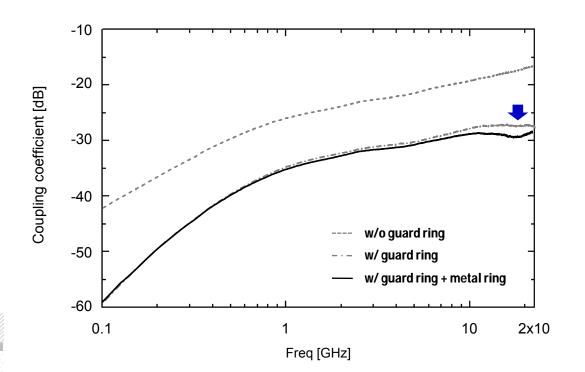

## Shielding Effect Measurement – (1) Metal Ring

< Equivalent circuit model of coupled TSV>

• Metal ring has shielding effect only in high frequency because it blocks coupling in IMD layer

Terahertz Interconnection and Package Laboratory **33**

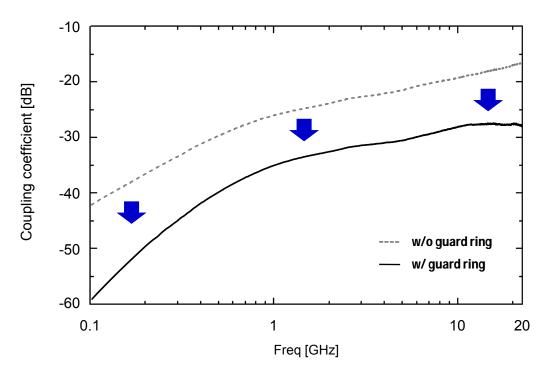

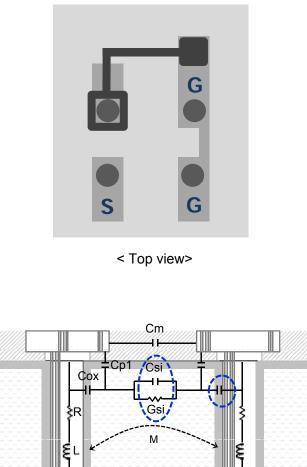

# Shielding Effect Measurement-(2) Guard Ring

< Top view>

< Equivalent circuit model of coupled TSV>

- Guard ring has good shielding effect in every frequency range because guard ring structure can partly block substrate coupling between TSVs

- Main factor of coupling between TSVs is silicon substrate

Terahertz Interconnection and Package Laboratory

34

# Shielding Effect Measurement-(3) Guard Ring + Metal Ring

< Equivalent circuit model of coupled TSV>

• Metal ring structure with guard ring can further decrease coupling between TSVs

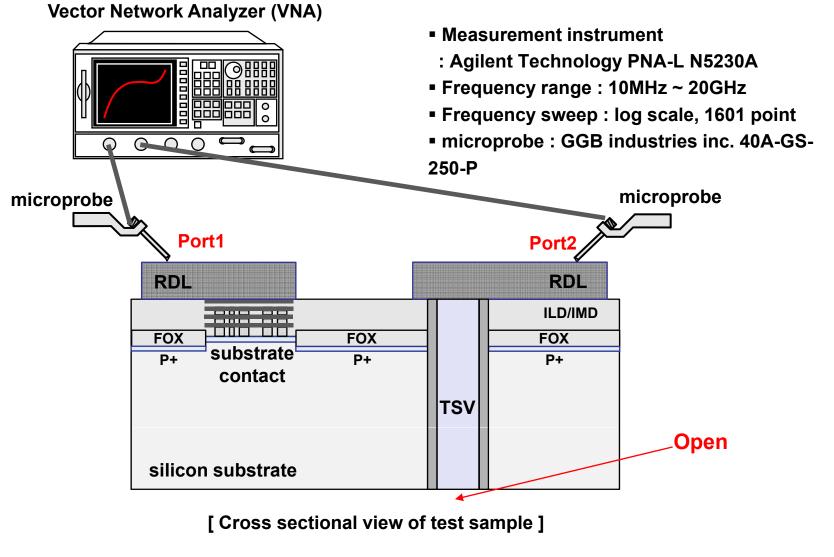

### **Measurement Environments for Model Verification**

KAIST

Terahertz Interconnection and Package Laboratory 36

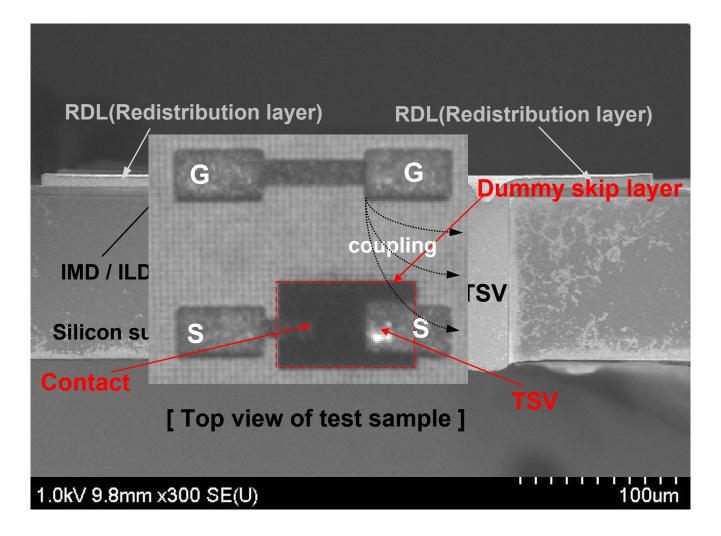

### **Designed Test Sample Images**

[Cross sectional view of test sample]

KAIST

Terahertz Interconnection and Package Labgratory 37

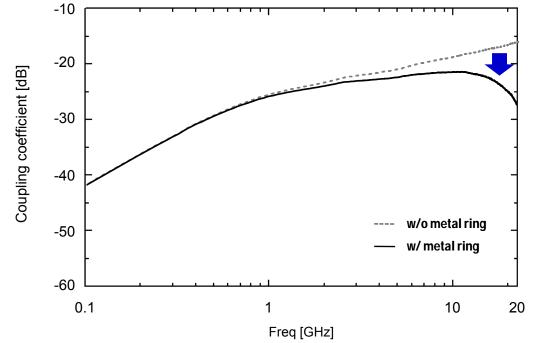

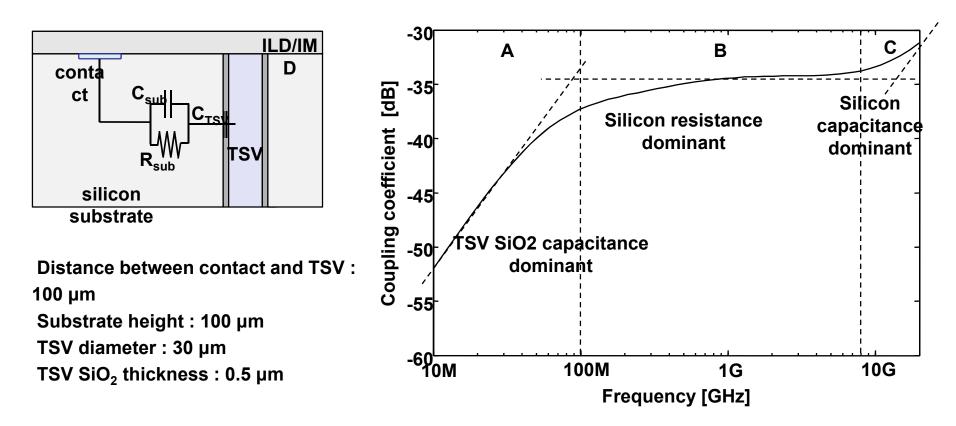

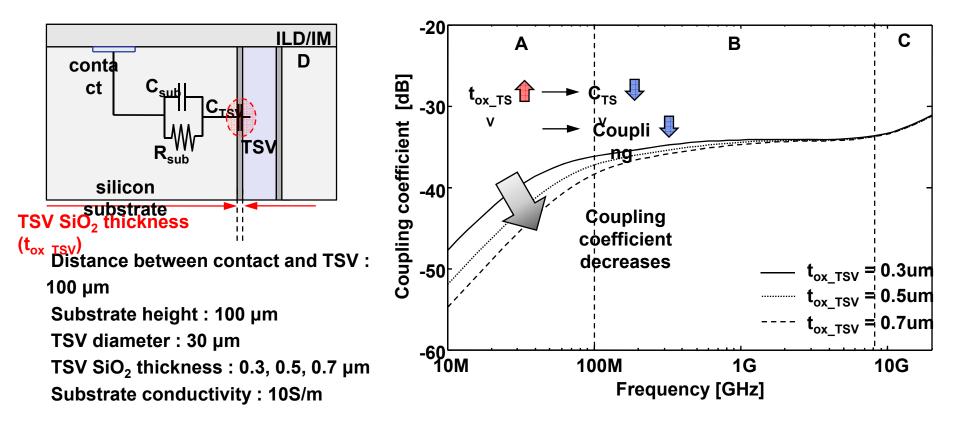

# Analysis of Noise Coupling based on the 3D TLM Model

- Coupling can be divided into 3-regions

- In region A, B, and C TSV SiO<sub>2</sub> capacitance, silicon resistance, silicon capacitance is the dominant factor to the coupling

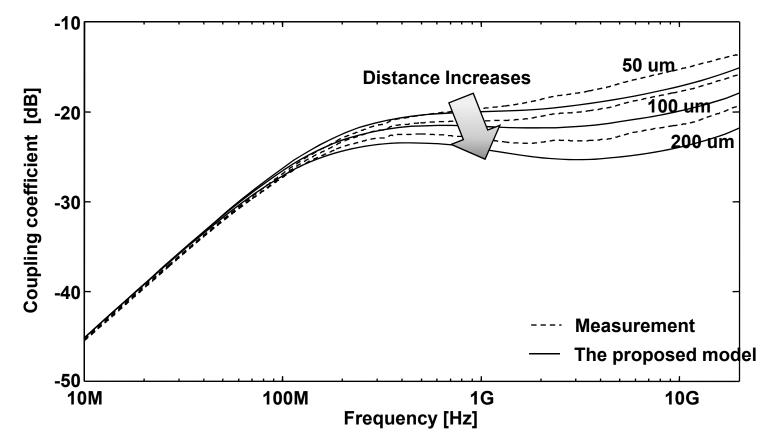

#### Substrate contact to TSV Coupling 3D TLM Model Verification by Measurement – with Distance Variation

Proposed model's coupling coefficient estimation is less than measurement over 1GHz

KAIST

But model follows same tendency as the distance increases

Terahertz Interconnection and Package Lab

#### Analysis of Noise Coupling based on the 3D TLM Model – with TSV SiO<sub>2</sub> Thickness Variation

- TSV SiO<sub>2</sub> thickness determine the coupling coefficient in the region A

- If we increases TSV SiO<sub>2</sub> thickness, coupling coefficient decreases in the region A

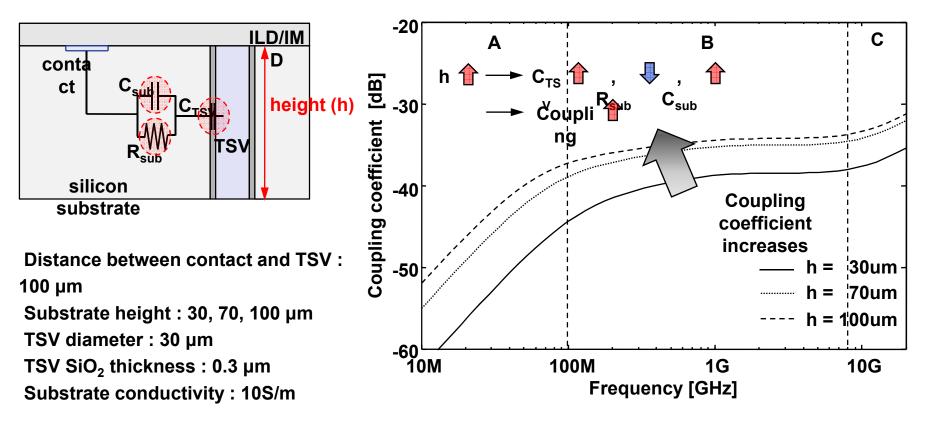

#### Analysis of Noise Coupling based on the 3D TLM Model – with Silicon substrate Height Variation (1)

- If silicon substrate height decreases, all component value is changed

- At the whole frequency, the coupling coefficient increases as silicon substrate height increases

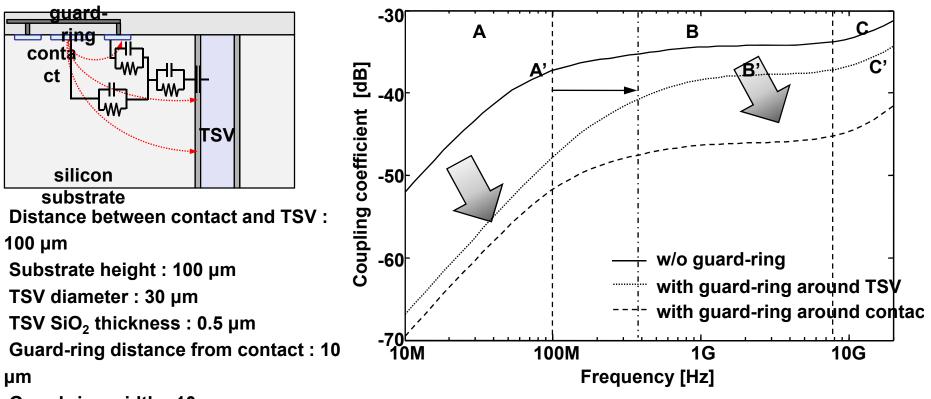

### Analysis of Guard-ring based on the 3D TLM Model – with Guard-ring Location Variation

Guard-ring width : 10  $\mu m$

- Guard-ring around contact shows more isolation effect compared to guard-ring around TSV

- Guard-ring around contact does not have frequency dependent isolation effect

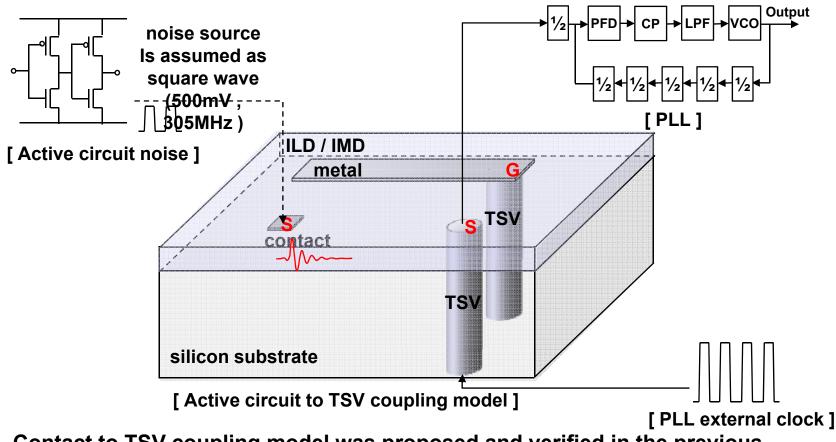

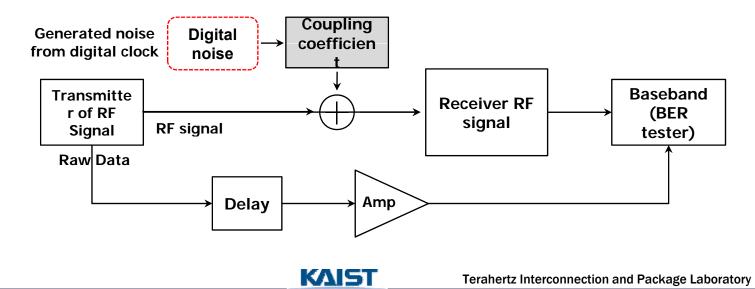

## **PLL Coupling Simulation Environment**

- Contact to TSV coupling model was proposed and verified in the previous chapter

- HSPICE simulation was performed using the contact to TSV coupling model and PLL schematic

TERA

Terahertz Interconnection and Package Labgretory

43

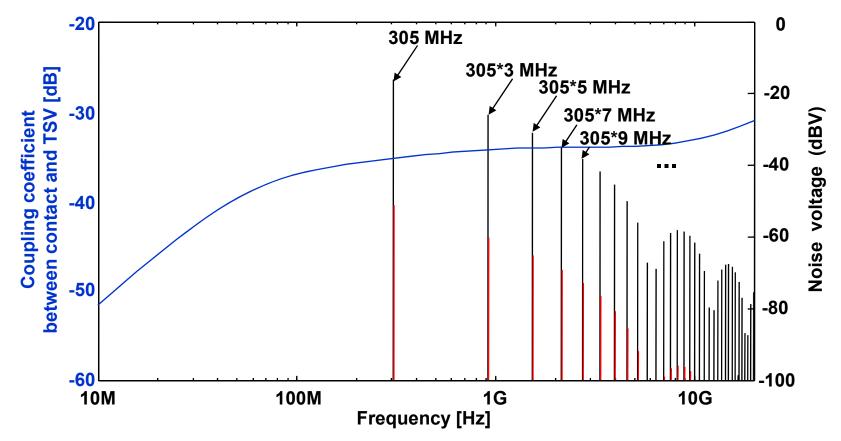

# Substrate Noise Coupling to TSV

• 305MHz square wave noise is coupled to TSV by the coupling coefficient

KAIST

Up to 9<sup>th</sup> harmonic frequency, coupling coefficient is almost constant

Terahertz Interconnection and Package Labgratory 44

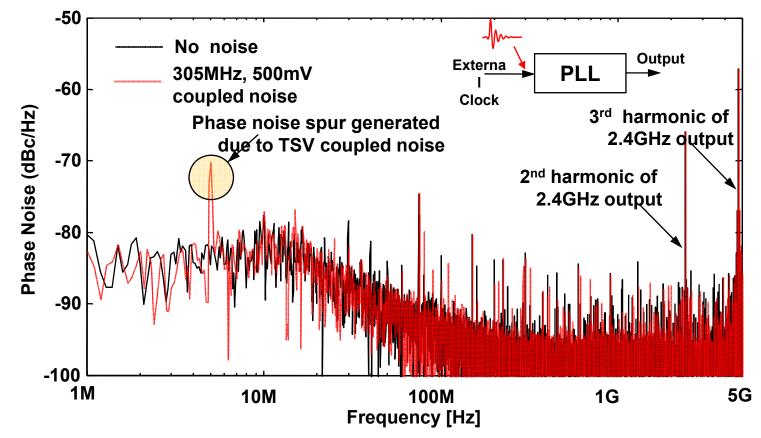

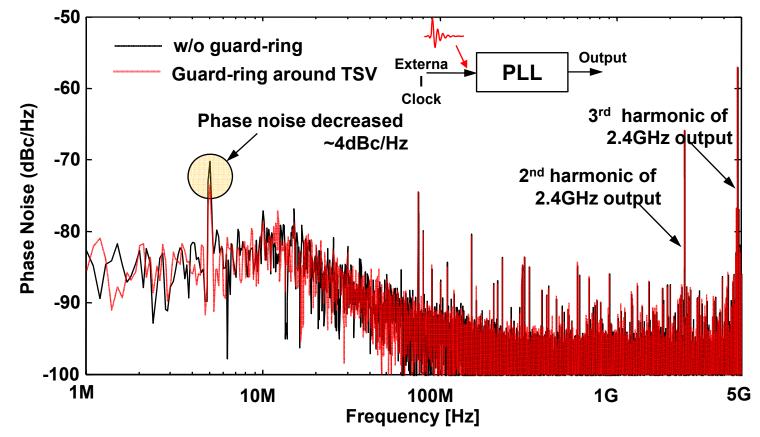

# PLL Phase Noise Degradation due to Active Circuit to TSV Coupling

- PLL phase noise shows spurs at 5MHz due to coupled 305MHz noise

- PLL phase noise spur at 75MHz, 2.4GHz, 4.8GHz is due to circuit design

TERRA Terahertz Inferconnection and Package Laboratory

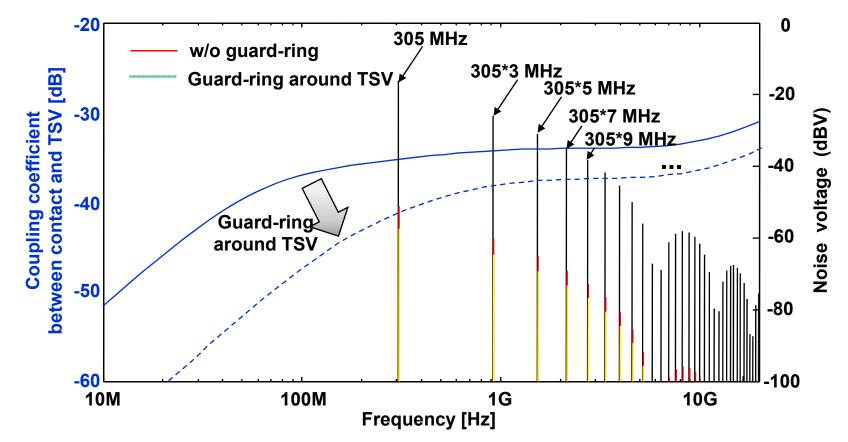

# Substrate Noise Coupling to TSV

- Guard-ring around TSV decreased coupling coefficient

- PLL coupled noise also decreased by the guard-ring around TSV

# PLL Phase Noise Degradation due to Active Circuit to TSV Coupling

- PLL phase noise spur at 5 MHz decreased by the guard-ring

- Guard-ring around TSV can improve coupling degraded circuit performance

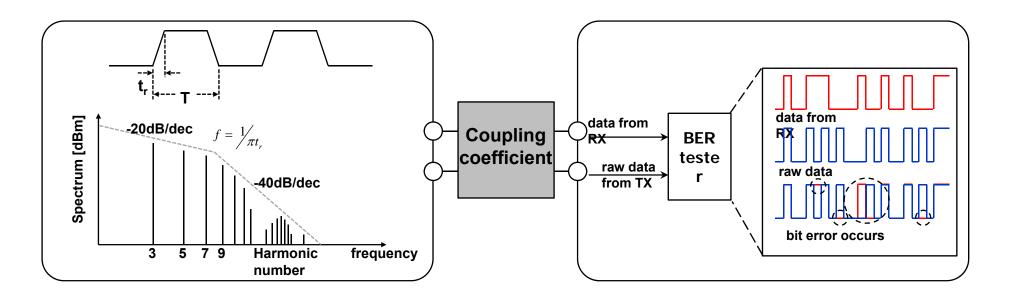

#### **BER Calculation in Mixed-Signal System Model**

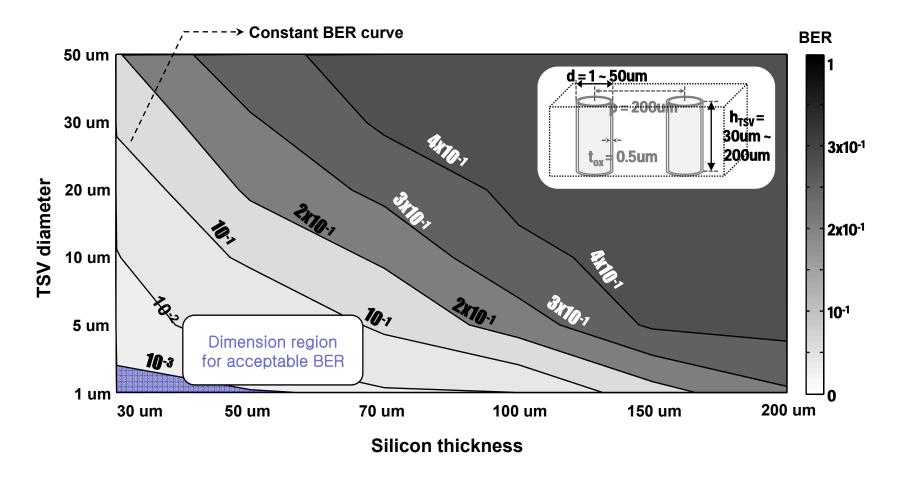

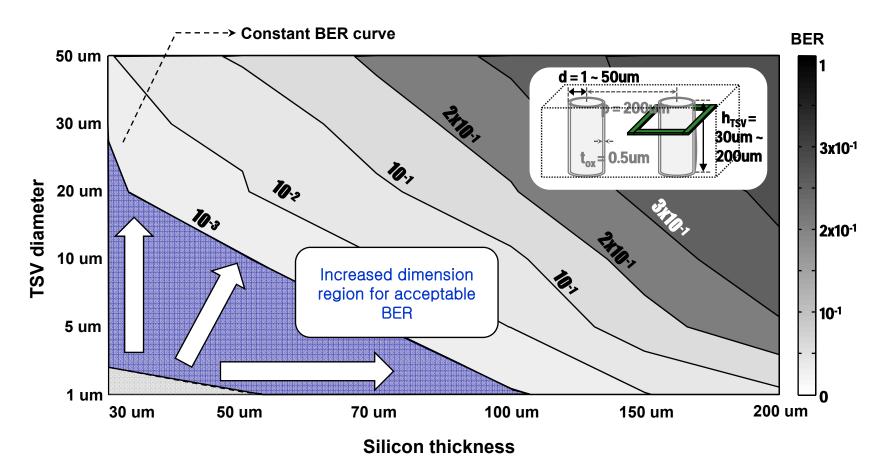

## **Dimension Region with Coupled TSV Parameters**

• In certain digital application, dimension region of TSV design parameters for acceptable BER can be obtained from the modeling of coupled TSVs

KAIST

Terahertz Interconnection and Package Laboratory 49

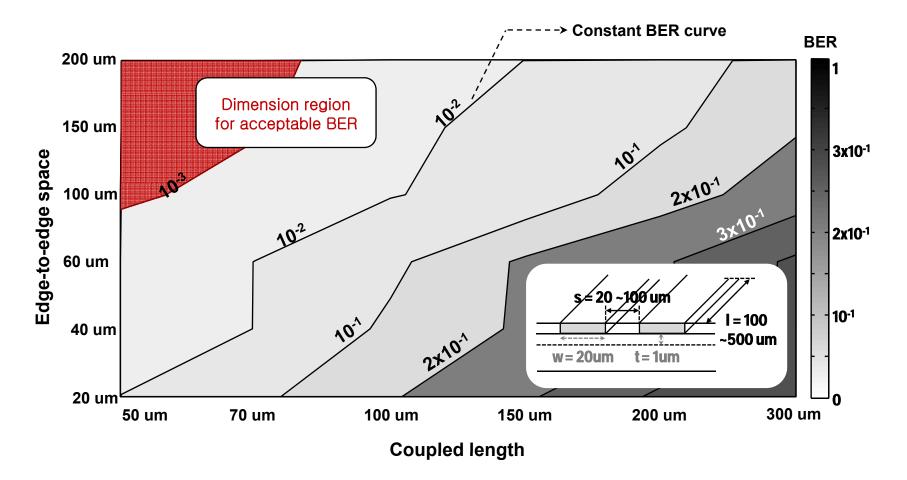

### Dimension Region with Coupled RDL Parameters

• In certain digital application, dimension region of RDL interconnects design parameters for acceptable BER can be obtained from the modeling of coupled RDL

KAIST

interconnects TERA Terahetz Interconnection and Package Laboratory

#### Dimension Region with Coupled TSV Parameters with Guard Ring

KAIST

- By applying guard ring structure, dimension region for acceptable BER is significantly increased

- → Target BER can be satisfied within realizable dimensions

RΔ

Terahertz Interconnection and Package Laboratory **51**

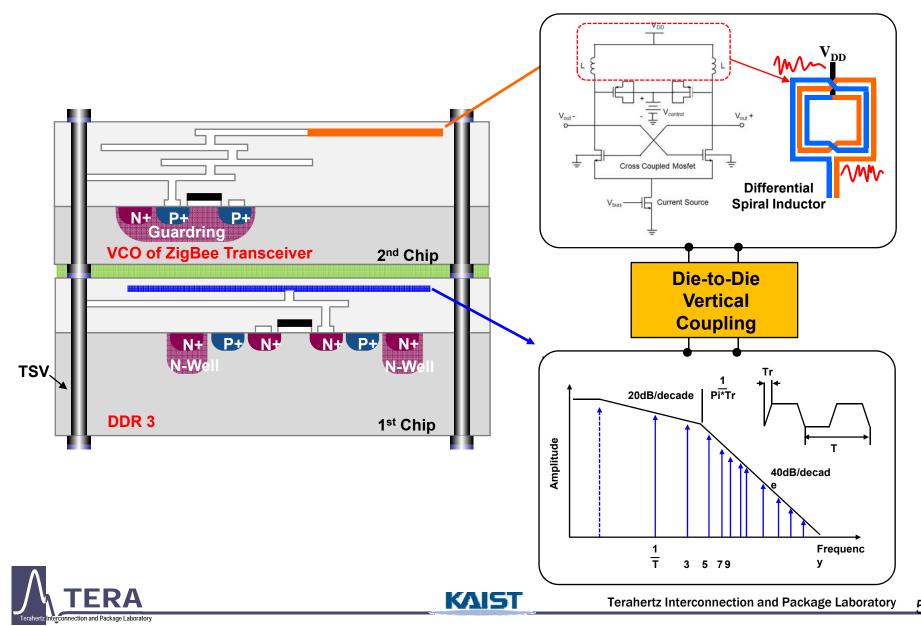

### Vertical Coupling of DDR3 to ZigBee Transceiver

<u>5</u>2

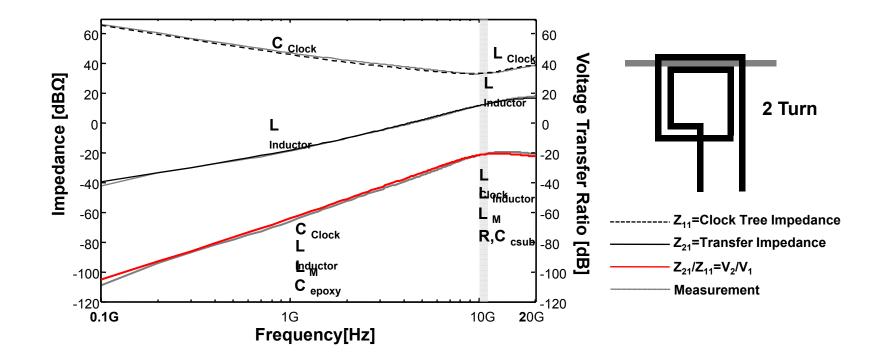

#### Experimental Verification of Proposed Model (Line Type Clock Tree to Two Turn Spiral Inductor)

- Before clock tree resonance, voltage transfer ratio is determined by C<sub>clock</sub> and L<sub>inductor</sub>.

- After clock tree resonance, voltage transfer ratio is determined by L<sub>clock</sub> and L<sub>inductor</sub>.

TERRA Terahertz Inferconnection and Package Laboratory

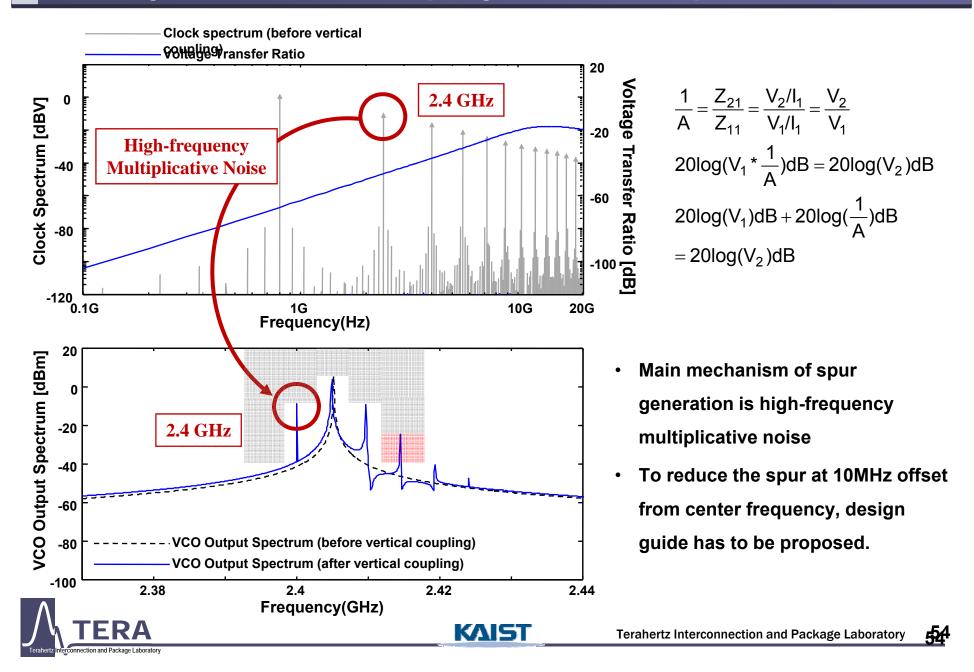

### **Investigation of Vertical Coupling Effect on VCO Spur**

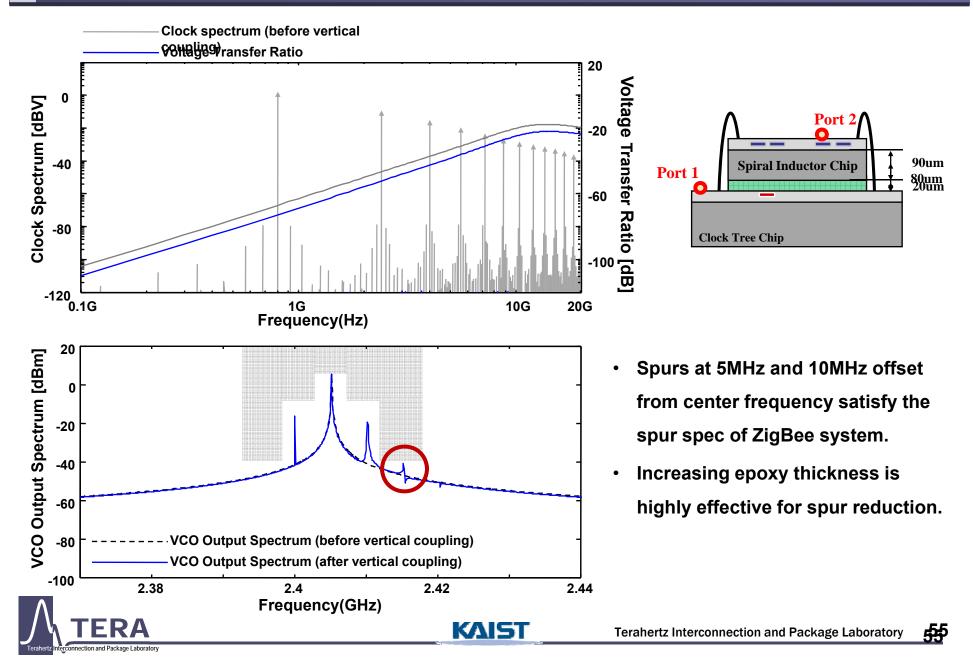

# Investigation of Design Guide for Spur Reduction (Epoxy Thickness)

-TSV is the most critical interconnection structure in 3D IC.

- TSV can cause significant channel loss for high-speed signaling.

- Equalizer or specific I/O schemes are needed to support low power and high-speed data transmissions.

- Crosstalk and coupling between TSV and active circuit need to be considered when designing the TSV arrangement configurations.

- Shielding structures are needed to reduce the TSV crosstalks and noise couplings.