# Project 1: Create Your Own WIMP51 Version

# **Objectives:**

Objectives were to create a version of WIMP51 processor in Quartus II which would include new instruction set, leaving the basic architecture of the processor intact. The instruction set assigned was CLRB A and SETB A, or clear bit in the accumulator and set bit in the accumulator, respectively.

### **Preliminary Analysis:**

Both, CLRB A and SETB A were two byte instructions. The operational code (op-code) for CLRB A was C2 expressed in hexadecimal numbers (11000010 in binary) and SETB A was

|               | · · · · · · · · · · · · · · · · · · · |         |

|---------------|---------------------------------------|---------|

| D2 in hexa    |                                       | n the   |

| accumulator   |                                       | egister |

| (IR) had to s |                                       | . Both  |

| bytes of info |                                       | d then  |

| passed into t |                                       |         |

| It wa         |                                       | a way   |

| similar to op |                                       | h was   |

| used to store |                                       | ess to  |

| the op-code   |                                       | to the  |

| accumulator   |                                       | order   |

| for cycle nat |                                       | attern  |

for cycle pattern to be copied to the new instruction set. Table 1 (below) described cycle pattern, or the register states and values contained for different cycles of Wimp51: fetch, decode, and execute, during the MOV A,#dd instruction set.

|               | I   |    |     |    |    | EC | UTE |                |

|---------------|-----|----|-----|----|----|----|-----|----------------|

| IR_WE         | ON  |    |     |    |    |    | 74  | IR             |

| <b>REG_WE</b> | OFF |    |     |    |    |    | XX  | <b>REG_TOP</b> |

| AUX_WE        | OFF |    |     |    |    |    | dd  | AUX            |

| PC_WE         | OFF |    |     |    |    |    | 1   | PC_ALU/PC      |

| ACC_WE        | OFF | XX | OFF | XX | ON |    | dd  | ACC            |

Table 1. Register states and values for different cycles during MOV A,#dd instruction

| From            | only instruction register write |

|-----------------|---------------------------------|

| enable logic (  | le logic units were in the OFF  |

| state. Thus, tl | R. During decode and execute    |

| cycles, the II  | t value 74H. Program counter    |

| write enable l  | C) was increased in the decode  |

| cycle. Thus, the          |   | er.   | This memo                    | ry regist                 | er stored the v             | alue   |

|---------------------------|---|-------|------------------------------|---------------------------|-----------------------------|--------|

| #dd to be move            |   | deo   | code cycle                   | the auxil                 | liary register v            | vrite  |

| enable logic (Al          |   | yte   | #dd was sto                  | ored in th                | e AUX registe               | er. In |

| the execute cyc           |   | : (/  | ACC_WE)                      | was in t                  | he ON state.                | This   |

| allowed for the           |   | r, te | o be moved                   | l in to th                | e accumulator               | . PC   |

| was again increi          |   | kt c  | p-code.                      |                           |                             |        |

| From the                  | 3 | on    | and the reg                  | gister stat               | tes, it was obv             | vious  |

| the new instruct          |   | ite   | enable logic                 | states for                | or the same cy              | cles.  |

| Hence the logic           |   | ΒA    | A should hav                 | ve been a                 | s shown in tab              | le 2.  |

|                           |   |       |                              |                           |                             |        |

|                           |   |       |                              |                           |                             |        |

|                           |   |       | EXECU                        | UTE                       |                             |        |

|                           |   |       | EXECU                        |                           |                             |        |

| IR_WE                     |   |       | EXECU<br>OFF                 | UTE<br>C2                 | IR                          |        |

| IR_WE<br>REG_WE           |   |       |                              |                           | IR<br>REG_TOP               |        |

| REG_WE                    |   |       | OFF                          | <b>C2</b>                 |                             |        |

| REG_WE<br>AUX_WE          |   |       | OFF<br>OFF                   | C2<br>xx                  | REG_TOP<br>AUX              |        |

| REG_WE<br>AUX_WE<br>PC_WE |   |       | OFF<br>OFF<br>ON             | C2<br>xx<br>0d            | REG_TOP<br>AUX<br>PC_ALU/PC |        |

| REG_WE<br>AUX_WE          |   | cy    | OFF<br>OFF<br>ON<br>ON<br>ON | C2<br>xx<br>0d<br>↑<br>dd | REG_TOP<br>AUX              |        |

## **Instruction Set Modifications:**

The instructions added were CLRB A, with an op-code C2 in hex or 11000010 in binary, and SETB A, with an op-code D2 in hex or 11010010 in binary. It was obvious these two were different only in bit-4. Hence, the modifications were same throughout most of the processor for both op-codes, except in the end where the chosen bit was either cleared (set to 0) or set to 1.

Instruction Register Modifications

| 0                   | 5    |             |

|---------------------|------|-------------|

| The instruc         |      | and in the  |

| OFF state for all c |      | de for IR   |

| or IR_WE logic. I   |      | This code   |

| was kept there al   |      | ring both,  |

| decode and execut   |      | -           |

|                     |      |             |

| Register Top Mod    |      |             |

| No modifi           |      | sters from  |

| R0 to R7 were not   |      |             |

|                     |      |             |

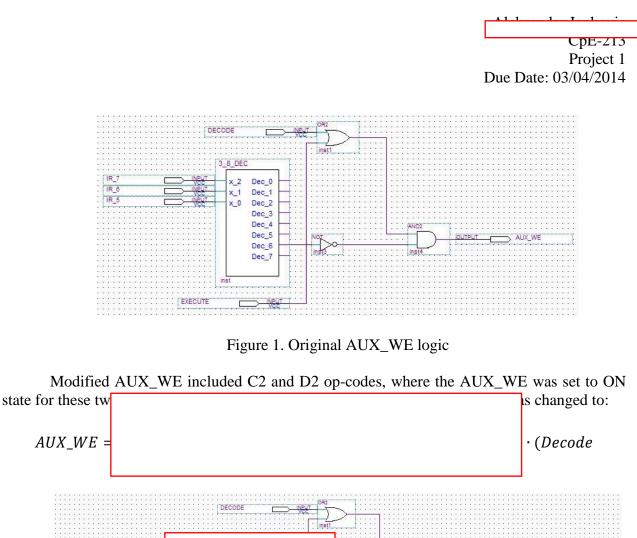

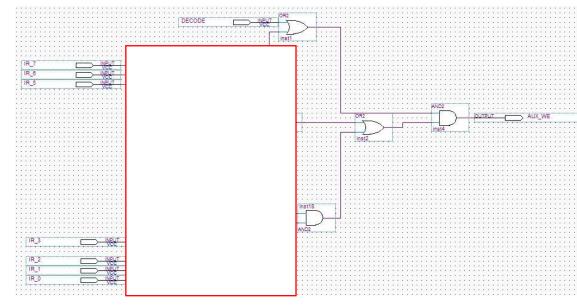

| Auxiliary Register  |      |             |

| Auxiliary           |      | structions. |

| However, auxiliar   |      | op-codes.   |

| In its original ve  |      | ave been    |

| expressed as follow | /ed: |             |

|                     |      |             |

Figure 2. Modified AUX\_WE logic

# Program Counter Modifications

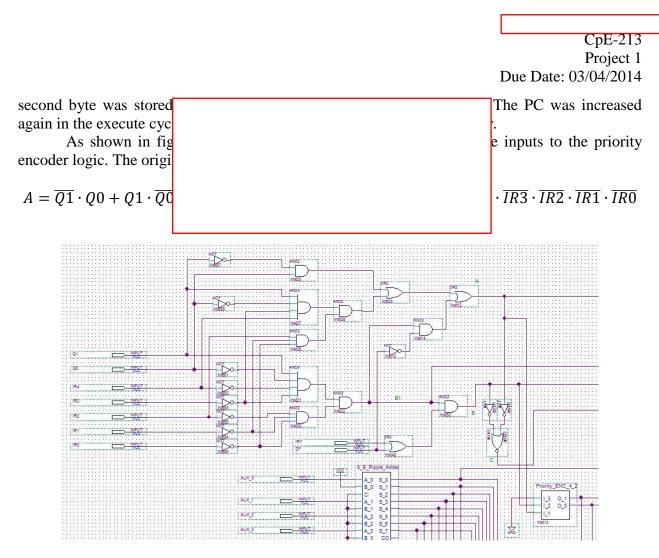

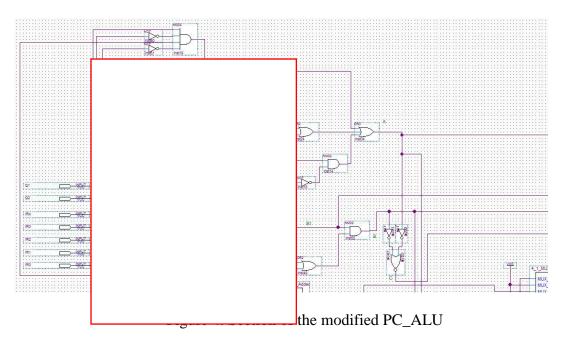

Since the new instructions were two byte long PC\_ALU and the PC\_WE had to be modified to accept new instructions. After the fetch cycle, where the op-code was stored in the IR, the PC had to be increased in the decode cycle to point at the second byte of the instruction. The second byte contained the information on the accumulator byte to be cleared or set. This

Figure 3. Section of the original PC\_ALU

The modified version of the PC\_ALU was shown in figure 4. After the analysis of the equation for the original fetch cycle (since Q1=0 execute cycle the output instruction. This modifica changed to:  $A_{modifi}$

The modified PC

e A-section was set to

high for the execute cycle, just as for the MOV A,#dd instruction. No other modifications in the PC\_ALU were necessary.

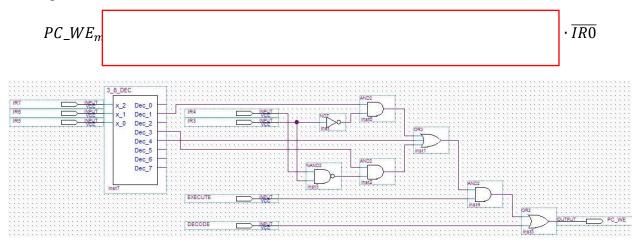

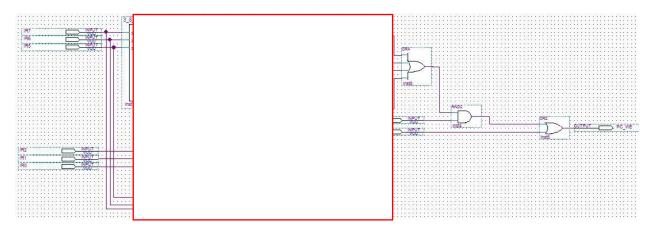

Original PC\_WE logic was setup to be in the ON state for decode cycle and for only certain instructions in the execute cycle. This was shown in figure 5 (below). Modified PC\_WE was setup with additional logic so it would include instructions C2 and D2 in the execute cycle. The logic added was shown below:

Figure 5. Original PC\_WE logic

Figure 6. Modified PC\_WE logic

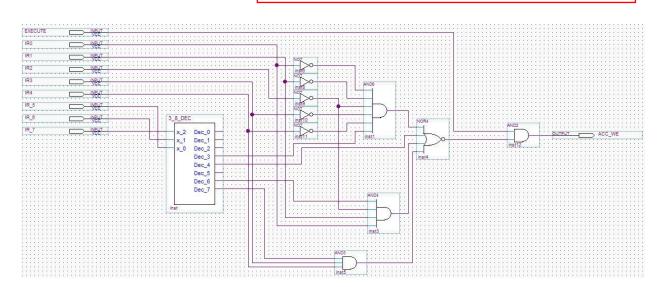

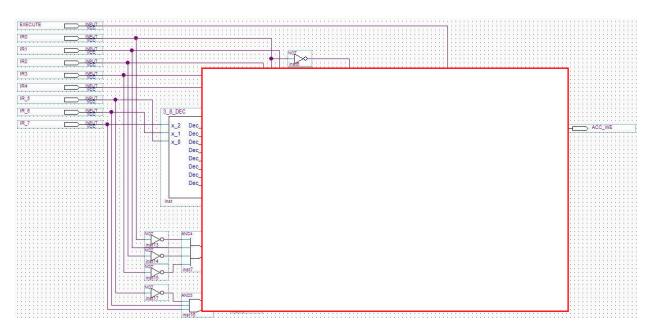

## Accumulator Register Modifications

There were no changes to the accumulator register However ACC WE had to be modified to include the new instrue ACC\_WE logic, respectively. The l enable for the accumulator was in th change this, but merely added two ne

$ACC\_WE_{modified} = ACC\_WE_{ort}$

Figure 7. Original ACC\_WE logic

Figure 8. Modified ACC\_WE logic

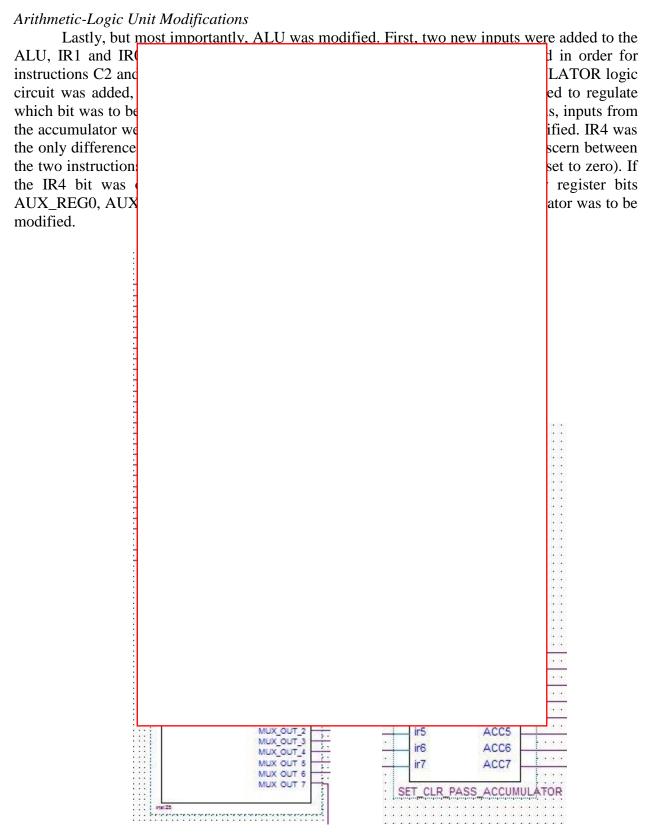

Figure 9. Modified ALU (left) and added SET\_CLR\_PASS\_ACCUMULATOR logic (right)

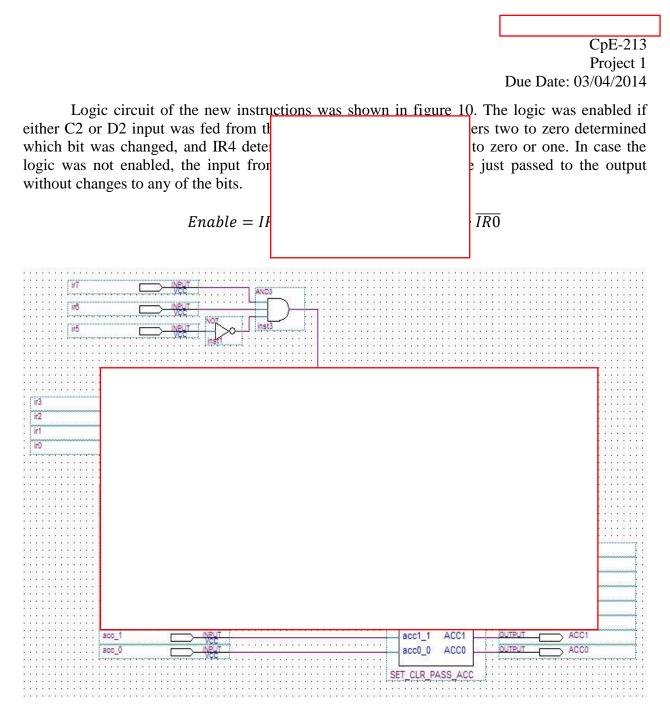

Figure 10. SET\_CLR\_PASS\_ACCUMULATOR logic

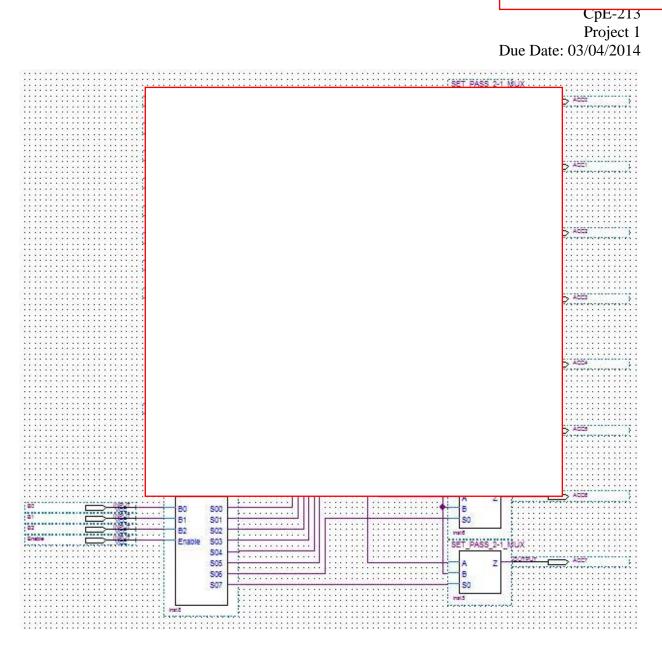

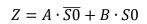

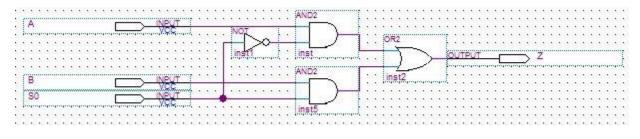

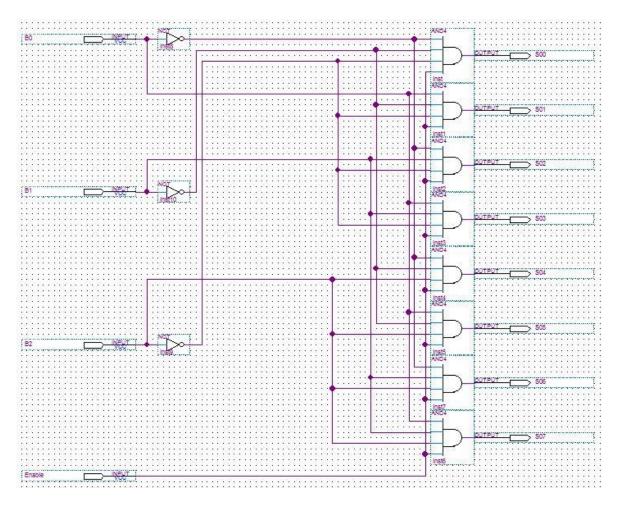

The inside of the SET\_CLR\_PASS\_ACC symbol file was shown in figure 11. It was noticeable the logic consisted of: accumulator inputs, 3:8-decoder, and eight 2:1 MUX logic units. The accumulator inputs were fed into the MUX units, where they were passed or changed. Decoder was used to determine the bit to be changed, by setting the input S0 of one of the MUX units to one. All the other would have input zero. Table 3 presented the logic behind the decoder. As explained before, if the enable input was set to one (using instruction register), the inputs of the auxiliary register decided which S0 input of the MUX units was set to high. Same unit changed the accumulator bit to one or zero, depending on the IR4 bit. Figure 13 showed the decoder logic. Lastly, 2:1 MUX units either passed or changed the accumulator bit. Logic was shown in figure 12 below.

Figure 11. Inside the SET\_CLR\_PASS\_ACC logic

Figure 12. MUX 2:1 logic

|        |   |   |   |   |   |   |   |    | 240 | Dui | 0.00 | / 0-1/ 2 |

|--------|---|---|---|---|---|---|---|----|-----|-----|------|----------|

| Enchlo |   |   |   |   |   |   |   | S  | 0   |     |      |          |

| Enable | Α |   |   |   |   |   |   | b4 | b3  | b2  | b1   | b0       |

| 0      |   |   |   |   |   |   |   | 0  | 0   | 0   | 0    | 0        |

| 1      |   |   |   |   |   |   |   | 0  | 0   | 0   | 0    | 1        |

| 1      |   |   |   |   |   |   |   | 0  | 0   | 0   | 1    | 0        |

| 1      |   |   |   |   |   |   |   | 0  | 0   | 1   | 0    | 0        |

| 1      |   |   |   |   |   |   |   | 0  | 1   | 0   | 0    | 0        |

| 1      |   |   |   |   |   |   |   | 1  | 0   | 0   | 0    | 0        |

| 1      |   |   |   |   | - | + | • | 0  | 0   | 0   | 0    | 0        |

| 1      |   | 1 | 1 | 0 | 0 | 1 | 0 | 0  | 0   | 0   | 0    | 0        |

| 1      |   | 1 | 1 | 1 | 1 | 0 | 0 | 0  | 0   | 0   | 0    | 0        |

Table 3. Decoder 3:8 of the SET\_CLR\_PASS\_ACC logic

Figure 13. Decoder 3:8 logic

Besides already described SET\_PASS\_CLR\_ACCUMULATOR logic circuit, two more were added to the ALU, as presented in figure 14. These were used to in order to keep the existing instructions unaffected and to prevent any overlapping of the new instructions with existing ones. Same 2:1 MUX units, shown in figure 12, were used to determine if the input from SET\_PASS\_CLR\_ACCUMULATOR logic were used, or if the old accumulator output logic was used. This was decided using LOG\_SETBA\_CLRBA logic unit, shown in figure 15. Boolean logic of that circuit was shown below.

Figure 15. LOG\_SETBA\_CLRBA unit

### **Testing the Modified WIMP51:**

**OP-CODE**

PC

DO

OD CODE

Three different programs were used in testing the modified WIMP51 processor. All three tested programs have given satisfactory (expected) results. First one used was to test the CLRB A instruction. This program was used to load hex number FF into the accumulator and then clear its bits one by one. The program was given here:

#### **CLRB A Test Program**

| rC         | OF-CODE |             |                                    |

|------------|---------|-------------|------------------------------------|

| 00         | 74      | MOV A, #FF  | ;Store FF into accumulator, ACC=FF |

| 01         | FF      |             | ;ACC=FF                            |

| 02         | C2      | CLRB A, #00 | ;Clear bit 0 of the accumulator    |

| 03         | 00      |             | ;ACC=FE                            |

| 04         | C2      | CLRB A, #01 | ;Clear bit 1 of the accumulator    |

| 05         | 01      |             | ;ACC=FC                            |

| 06         | C2      | CLRB A, #02 | ;Clear bit 2 of the accumulator    |

| 07         | 02      |             | ;ACC=F8                            |

| 08         | C2      | CLRB A, #03 | ;Clear bit 3 of the accumulator    |

| 09         | 03      |             | ;ACC=F0                            |

| <b>0</b> A | C2      | CLRB A, #04 | ;Clear bit 4 of the accumulator    |

| 0B         | 04      |             | ;ACC=E0                            |

| 0C         | C2      | CLRB A, #05 | ;Clear bit 5 of the accumulator    |

| 0D         | 05      |             | ;ACC=C0                            |

| <b>0E</b>  | C2      | CLRB A, #06 | ;Clear bit 6 of the accumulator    |

| <b>0F</b>  | 06      |             | ;ACC=80                            |

| 10         | C2      | CLRB A, #07 | ;Clear bit 7 of the accumulator    |

| 11         | 07      |             | ;ACC=00                            |

| 12         | 80      | SJMP rel    | ;Jump back to here                 |

| 13         | FE      |             |                                    |

Second testing program, shown below, was used to load hex number 00 into the accumulator and then set its bits one by one, thus ending with the accumulator value of FF. The program was given here:

#### SETB A Test Program

| PC | OP-CODE |             |                                    |

|----|---------|-------------|------------------------------------|

| 00 | 74      | MOV A, #FF  | ;Store 00 into accumulator, ACC=00 |

| 01 | 00      |             | ;ACC=00                            |

| 02 | D2      | SETB A, #00 | ;Set bit 0 of the accumulator      |

| 03 | 00      |             | ;ACC=01                            |

| 04 | D2      | SETB A, #01 | ;Set bit 1 of the accumulator      |

| 05 | 01      |             | ;ACC=03                            |

| 06        | D2 | SETB A, #02 | ;Set bit 2 of the accumulator |

|-----------|----|-------------|-------------------------------|

| 07        | 02 |             | ;ACC=07                       |

| 08        | D2 | SETB A, #03 | ;Set bit 3 of the accumulator |

| 09        | 03 |             | ;ACC=0F                       |

| 0A        | D2 | SETB A, #04 | ;Set bit 4 of the accumulator |

| 0B        | 04 |             | ;ACC=1F                       |

| 0C        | D2 | SETB A, #05 | ;Set bit 5 of the accumulator |

| 0D        | 05 |             | ;ACC=3F                       |

| <b>0E</b> | D2 | SETB A, #06 | ;Set bit 6 of the accumulator |

| <b>0F</b> | 06 |             | ;ACC=7F                       |

| 10        | D2 | SETB A, #07 | ;Set bit 7 of the accumulator |

| 11        | 07 |             | ;ACC=FF                       |

| 12        | 80 | SJMP rel    | ;Jump back to here            |

| 13        | FE |             |                               |

The last test program was used to make sure no other instructions were affected by the modifications. This program was given here:

|           | CLRBA a        | and SETB A Test Pro | ogram                                          |

|-----------|----------------|---------------------|------------------------------------------------|

| PC        | <b>OP-CODE</b> |                     |                                                |

| 00        | 74             | MOV A, #FF          | ;Store 01 into accumulator, ACC=01             |

| 01        | 01             |                     | ;ACC=01                                        |

| 02        | F8             | MOV R0,A            | ;R0=ACC=01                                     |

| 03        | 38             | ADDC A,R0           | ;ACC=ACC+R0=02                                 |

| 04        | D2             | SETB A, #03         | ;Set bit 3 of the accumulator                  |

| 05        | 03             |                     | ;ACC=0A                                        |

| 06        | F9             | MOV R1,A            | ;R1=ACC=0A                                     |

| 07        | C4             | SWAP A              | ;Swap upper and lower and upper nibble, ACC=A0 |

| 08        | C2             | CLRB A, #05         | ;Clear bit 5 of the accumulator                |

| 09        | 05             |                     | ;ACC=80                                        |

| <b>0A</b> | FA             | MOV R2,A            | ;R2=ACC=80                                     |

| <b>0B</b> | 80             | SJMP rel            | ;Jump back to here                             |

| 0C        | FE             |                     |                                                |

#

#### **Conclusion:**

In this project WIMP51 processor was modified and tested on the Altera board. The task was to add two more instructions, CLRB A and SETB A, which would access accumulator and clear or set one bit at the time. This was done by modifying: auxiliary register and its write enable logic, program counter ALU and the program counter write enable, accumulator write enable logic, and the ALU. These modifications were tested using three different programs, which have given expected results, thus proving the functionality of the modified WIMP51.